Beschleunigte Alterung im Einschaltmodus von selbstsperrenden GaN-Transistoren

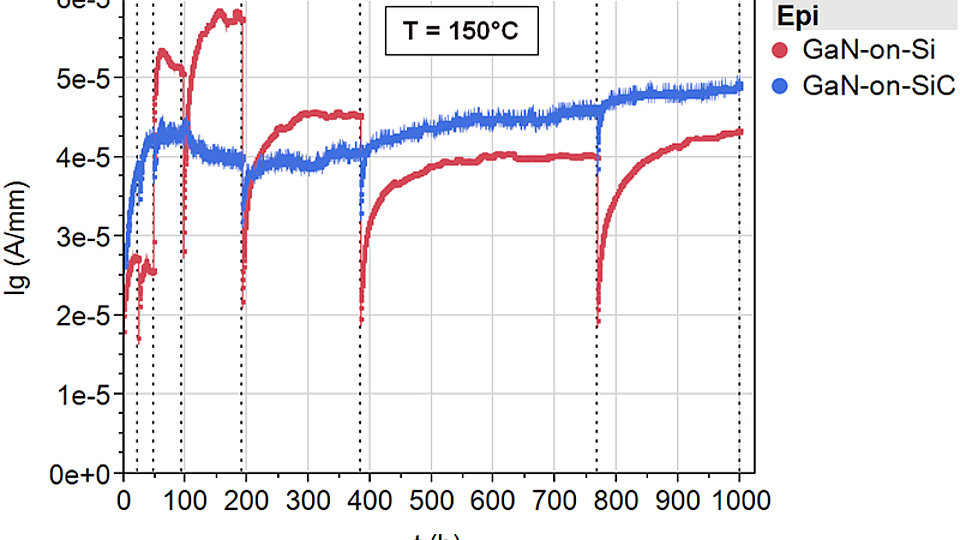

Abb. 2: Gatestromtransiente für GaN-auf-SiC- (blau) und GaN-auf-Si- (rot) Transistoren während 1000 h Alterung. Messungen wurden zur DC-Charakterisierung (gestrichelte Linie) unterbrochen

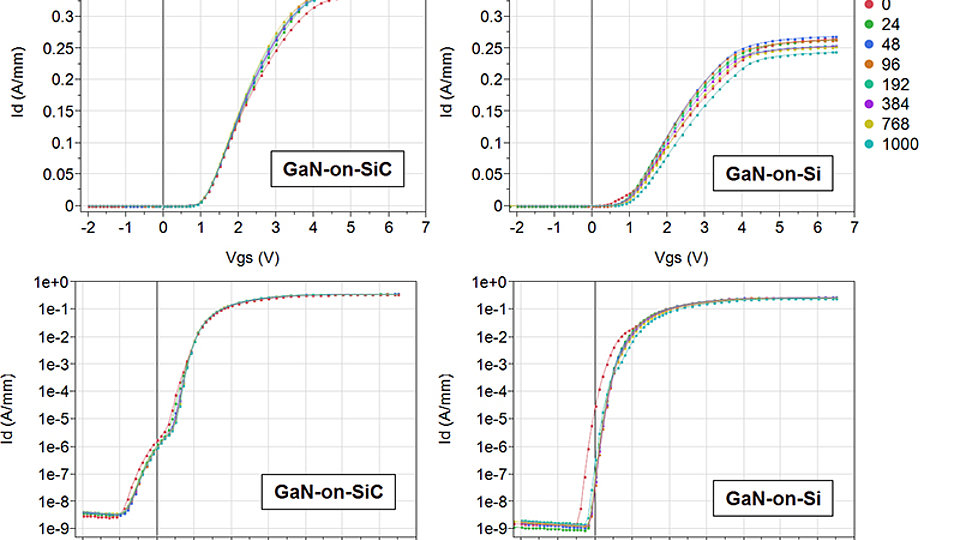

Abb. 3: Entwicklung der DC-Eingangskennlinien für GaN-auf-SiC- (li.) und GaN-auf-Si- (re.) Transistor während 1000 h Alterung, linearere (o.) und logarithmische (u.) Darstellung. Vds = 10 V

GaN-basierte Leistungstransistoren für hohe Spannungen ermöglichen dank ihres geringen flächenspezifischen Einschaltwiderstands und der geringen Schaltverluste effiziente Leistungskonverter mit besonders hoher Leistungsdichte. Dafür ist selbstsperrendes Verhalten der Transistoren erforderlich. Um dieses bei GaN-Hochspannungs-HFETs zu erreichen, setzt das FBH ein p-GaN-Gatemodul ein. Dabei bildet das p-dotierte GaN-Gate einen Halbleiterkontakt zum n-leitfähigen GaN-Kanal, der durch die AlGaN-Barriere vom Gate getrennt ist, welches pin-Diodeneigenschaften aufweist. Andere Ansätze bei GaN-HFETs nutzen ein Metallgate mit einem Schottkykontakt – ebenfalls mit Diodeneigenschaften – oder erzeugen mittels eines Dielektrikums ein elektrisch isoliertes Gate (MISFET).

Bereits zuvor, wurde die Zuverlässigkeit von GaN-basierten HFETs bei unterschiedlichen Betriebszuständen umfassend untersucht. Dies gilt insbesondere für die Belastung des gesperrten Transistors bei hohen Drainspannungen. Nun analysierte das FBH zusätzlich die Zuverlässigkeit der selbstsperrenden p-GaN-Gate-Transistoren im eingeschalteten Zustand. Dabei fließt bei 5 V Gatespannung ein kleiner Strom durch die pin-Gatediode. Es ist daher zu erwarten, dass sich eventuelle Alterungseffekte von Transistoren mit diesem Gatemodul von den Alterungseffekten konkurrierender Ansätze wie Schottky-Gate-Transistoren oder MISFETs unterscheiden.

Testtransistoren mit 3,2 mm Gateweite wurden bei geöffnetem Gate (Vg = 5 V) entsprechend der Bedingungen für den eingeschalteten Zustand im Schaltbetrieb mit 50 mA/mm Drainstrom (Vds ~ 1,5 V) 1000 Stunden lang betrieben. Zur Beschleunigung von Alterungseffekte wurde die Umgebungstemperatur auf 150°C erhöht. Die DC-Eigenschaften der Probanden wurden vor, nach und 6x innerhalb der Stressperiode gemessen. Transistoren mit einem unterschiedlichen (Al)GaN-Schichtenaufbau auf SiC- oder Si-Substraten wurden verglichen.

Während der ersten 50 Stunden verdoppelt sich der Gatestrom für beide untersuchten Bauelemente. Der Gatestrom für den GaN-auf-SiC-Transistor nimmt dann während der 1000 h Alterungsbetrieb um weitere 25% zu. Im Gegensatz dazu zeigt der GaN-auf-Si-Transistor starke Gatestromfluktuationen. So dauert es immer etwa 100 Stunden, bis nach der Abkühlperiode für die zwischenzeitlichen DC-Messungen der Gatestrom seinen vorherigen Gleichgewichtswert wieder erreicht hat. Dies deutet auf eingefangene Ladungen an den pin-Kontaktflächen hin. Für den GaN-auf-SiC-Transistor ändern sich während der 1000 h Belastung der Drain-Sperrleckstrom, die Einsatzspannung und der maximale Drainstrom nicht. Eine Einsatzspannungsverschiebung von +0,3 V (innerhalb der ersten 24 h) und eine Verringerung des Drainstroms um 11% während der kompletten Belastungszeit wurde aber für den GaN-auf-Si-Transistor beobachtet.

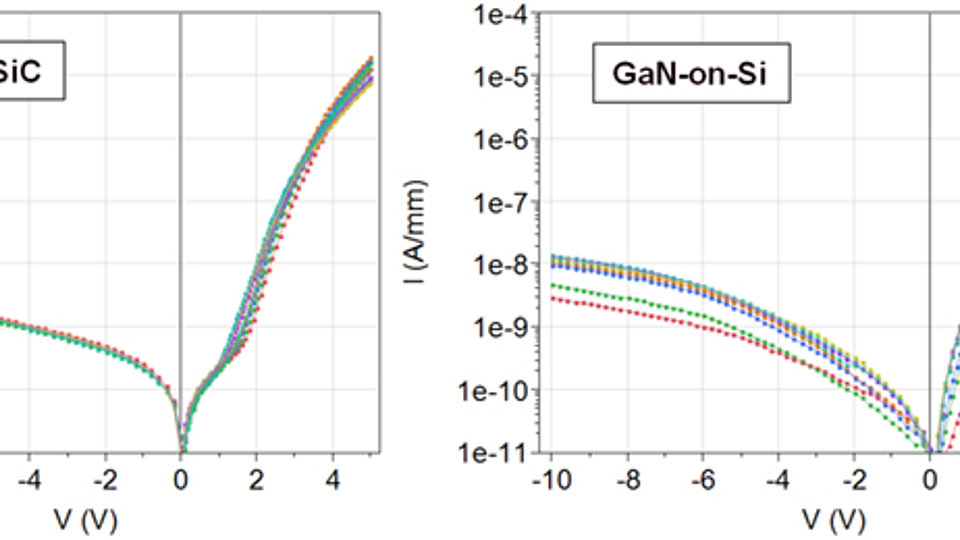

Prinzipielle Unterschiede zwischen diesen beiden Bauelementen zeigen sich in der Gatediode. Der Gatestrom bei 1 V Gatespannung erhöht sich für den GaN-auf-Si-Transistor innerhalb der ersten 96 h um den Faktor 30. Für den GaN-auf SiC-Transistor konnte aber nur eine Gatestromerhöhung um 50% innerhalb der kompletten 1000 h beobachtet werden. Die reduzierte Sperrfähigkeit der GaN-auf-Si-Gatediode zeigt sich im fünfmal erhöhten Sperrleckstrom bei -10 V Gatespannung.

Bei der hier beschriebenen Zuverlässigkeitsüberprüfung des p-GaN-Gatemoduls wurden selbstsperrende GaN-Schalttransistoren bei 150°C 1000 h lang bei geöffnetem Gate betrieben. Es wurde gezeigt, dass die Qualität der Grenzschichten zwischen GaN-Kanal, AlGaN-Barriere und p-dotiertem GaN-Gate wesentlich die Stabilität der Gatediode bestimmt. Eine Gatediodendegradation führt zu Verschiebungen in der Einsatzspannung und zu niedrigeren Drainströmen. Die GaN-auf-SiC-Technologie erweist sich dabei als degradationsfrei und eignet sich somit für leistungselektronische Anwendungen.

Publikationen:

O. Hilt, E. Bahat-Treidel, A. Knauer, F. Brunner, R. Zhytnytska, J. Würfl, "High-voltage normally OFF GaN power transistors on SiC and Si substrates", MRS Bull., vol. 40, no. 05, pp. 418-424 (2015).

M. Ťapajna, O. Hilt, E. Bahat-Treidel, J. Würfl, and J. Kuzmík, "Investigation of gate-diode degradation in normally-off p-GaN/AlGaN/GaN high-electron-mobility transistors", Appl. Phys. Lett., vol. 107, no. 19, pp. 193506 (2015).