Design, Herstellung, und Charakterisierung von miniaturisierten AuSn Flip-Chip-Übergängen bis 110 GHz

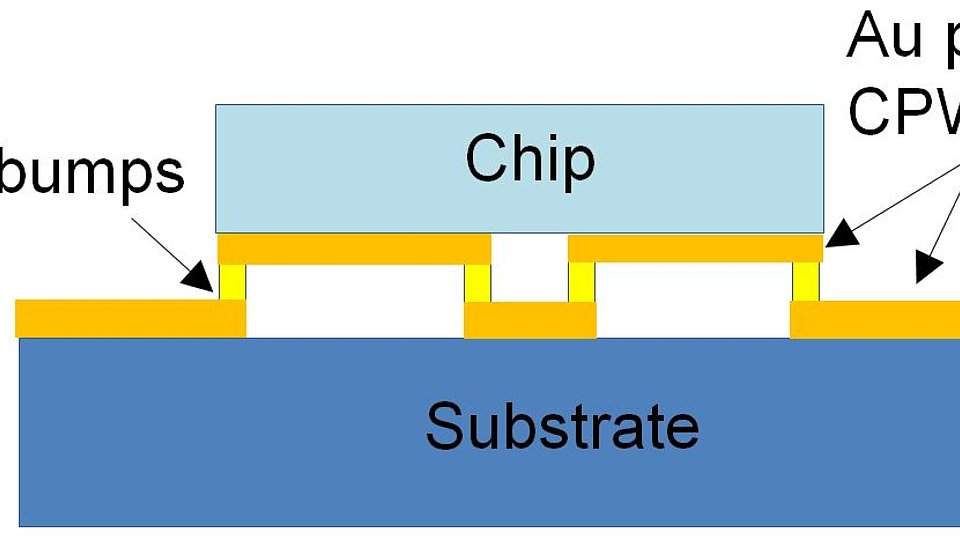

Die Flip-Chip-Technologie ist eine attraktive Lösung für die Aufbau- und Verbindungstechnik von Höchstfrequenzanwendungen – insbesondere verglichen mit der Bonddraht-Methode. Flip-Chip-Aufbauten (vgl. Abb. 1a) bieten im Gegensatz zu klassischen Hohlleiter-Aufbauten eine gute thermische und mechanische Stabilität. Die Übergänge ermöglichen geringere parasitäre Induktivitäten, größere Bandbreiten und können wegen der präzisen Fertigungstechnologie gut reproduziert und modelliert werden. Für die hier anvisierten Frequenzbereiche von 100 bis 350 GHz sind typische Abmessungen von Wellenleiterstreifen und Flip-Chip Bumps ~10 µm. Diese Abmessungen lassen sich mit Halbleiter-Fertigungstechniken präzise und kostengünstig fertigen.

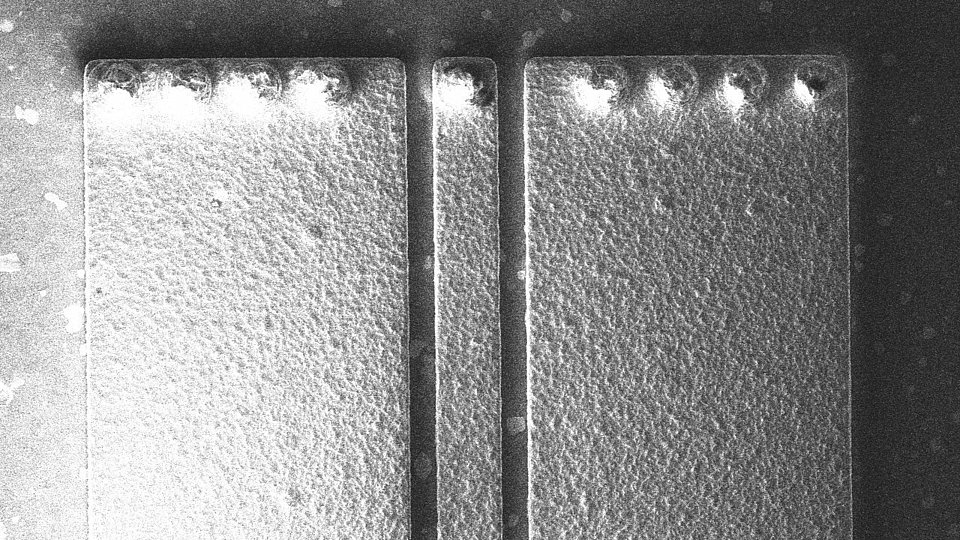

In dieser Arbeit wurde die Prozesstechnologie für sehr kleine AuSn-Bump Flip-Chip-Übergange mit einem Bumpdurchmesser von < 10 µm entwickelt. Die Koplanarwellenleiter (CPW) wurden durch Au-Galvanisierung sowohl auf dem Chip (Aluminumnitrid bzw. Quartz-Material) als auch auf dem Aluminumnitrid-Substrat hergestellt. Die AuSn-Bumps sind 6 µm dick und wurden als Multischicht mit dem Gehalt von 80% wt. Au und 20% wt. Sn von der Chipseite her auf die CPW aufgedampft. Die Strukturierung der Bumps erfolgte mit einem i-line Stepper und anschließender Lift-Off-Technik (vgl. Abb. 1b). Die Verbindung zwischen Chip und Substrat wurde auf einer kommerziellen Flip-Chip-Anlage (FC-150) mit einer lateralen Justiergenauigkeit von besser als 2 µm hergestellt. Die gemessenen Kleinsignal-Transmissionskurven zeigen einen graduell mit der Frequenz ansteigenden Verlust. Diese Verluste können hauptsächlich auf Leitungsverluste zurückgeführt werden.

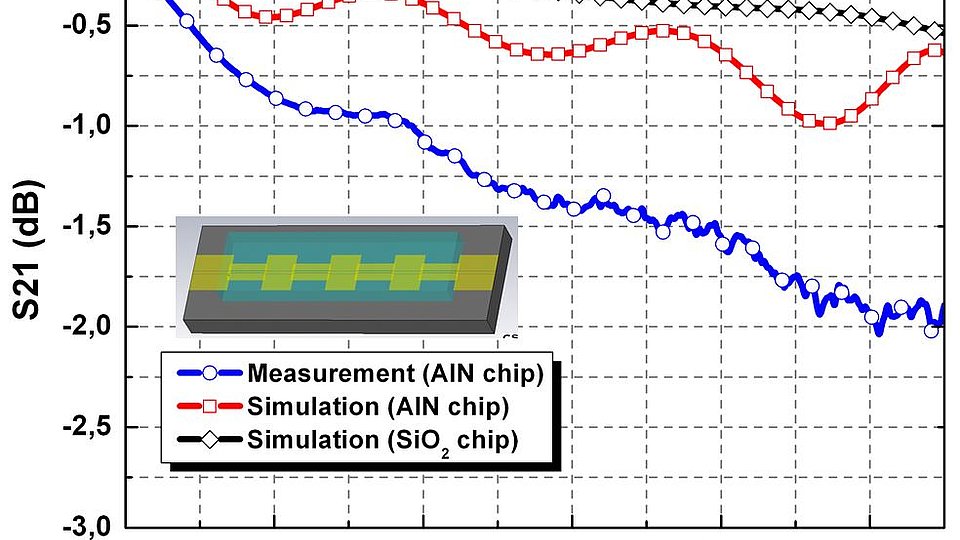

Unter Berücksichtigung der Leitungsverluste konnten durch Messung der S-Parameter die Einfügungsverluste der Flip-Chip-Übergänge bestimmt werden. Demnach ergeben sich für ein Bauteil mit insgesamt acht Übergängen bei 110 GHz eine Dämpfung von -2 dB (vgl. Abb. 2) und eine Reflektionsdämpfung von weniger als etwa -15 dB. Die gezeigte Simulation berücksichtigt die Ohmschen Verluste im Wellenleiter-Metall nicht, was die Diskrepanz zwischen simulierter und gemessener Kurve auf AlN erklärt. Um die Dämpfung in einem einzelnen Übergang abschätzen zu können, subtrahieren wir die Dämpfung einer Linie ohne Übergang, welche die gleiche Länge wie die gesamte Teststruktur aufweist. Eine Linie ohne Übergang zeigt eine Dämpfung von 1 dB bei 110 GHz – und liegt damit bei weniger als 0,5 dB pro Übergang. Der Reflektionsverlust und die Welligkeit der Transmissionskurve über der Frequenz kann durch Anpassung der Dimensionen der CPW-Linie weiter optimiert werden. Das hier gemessene Bauteil wurde für SiO2-Substrate berechnet. Allerdings wurden die getesteten Chips aus prozesstechnologischen Gründen auf AlN-Substraten hergestellt. Die Dielektrizitätskonstanten von SiO2 und AlN sind 3,8 und 8,9. Die Impedanz der auf AlN anstelle von SiO2 hergestellten Wellenleiter weicht von der berechneten Impedanz von 50 Ohm ab und führt zur Welligkeit in der Transmissionskurve.

Zusammenfassend lässt sich feststellen, dass sich kleine AuSn-Bumps (<10 μm) herstellen lassen. Die RF-Charakterisierung der Flip-Chip-Übergänge bis 110 GHz zeigt einen niedrigen Übergangsverlust von weniger als 0,5 dB pro Einzelübergang. Dieses Ergebnis bestätigt, dass die AuSn Flip-Chip-Technologie eine geeignete Packaging-Alternative für Millimeterwellen-Applikationen ist.

Publikation:

S. Monayakul, C. Wang, O. Krüger, N. Weimann, "Design, Fabrication, and Characterization of Miniaturized AuSn Flip-Chip Transitions up to 110 GHz", Proc. WOCSDICE 2013.

FBH-Forschung: 24.06.2013